Abstract:

On March 19, 2019, Zhou Fei, a master student of the BiCASL Laboratory of the Department of Micro-Nano Electronics, Shanghai Jiaotong University, attended the academic conference of China International Semiconductor Technology Conference (CSTIC 2019) held in Pudong, Shanghai.

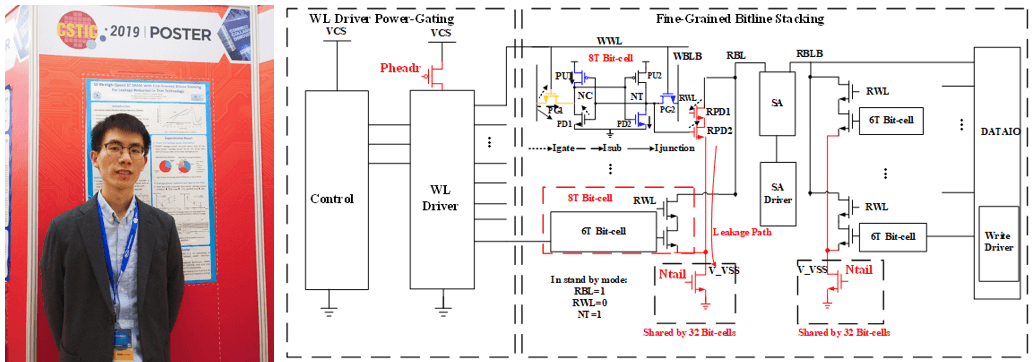

On March 19, 2019, Zhou Fei, a master student of the BiCASL Laboratory of the Department of Micro-Nano Electronics, Shanghai Jiaotong University, attended the academic conference of China International Semiconductor Technology Conference (CSTIC 2019) held in Pudong, Shanghai, and won the Best Poster Award. At the conference, Zhou Fei's paper "A 32-Kb High-speed 8T SRAM with Fine-grained Bitline Stacking for Leakage Reduction in 7nm Technology" was presented in the form of a poster and won the Best Poster Award. CSTIC is Asian largest world-class semiconductor technology seminar jointly organized by SEMI, IMEC, IEEE and China's high-tech experts.

Zhou Fei's paper shows a 32 Kb low leakage SRAM based on 8T memory cells. The paper proposes three technologies, Fine-grained Bitline Stacking, Bank-Level WL Driver Power-Gating and Floating Write Driver, which reduce the leakage power consumption of SRAM by 75% and sacrifice only 1% of the area. The low leakage SRAM has broad application prospects in the field of Internet of Things.